Speed and volatility O d. Speed and volatility b.

Direct Mapped Cache An Overview Sciencedirect Topics

First once one block is scan in another could be replaced.

. This preview shows page 15 - 20 out of 23 pages. These are as follows Cache Read Operation 1 Block Size Block size is the unit of information changed between cache and. The obvious ones are size and associativity.

B size and replacement policy. Course Title CIS 123. Size and replacement policy O c.

L2 or Level 2 Cache. Size and replacement policy ____ operating systems are designed primarily to maximize resource utilization. Answer- 1cache size and replacement policy 2round robin 3all of the above 4starvation 5shortest job first.

Compilers Vulnerability Energy efficiency Cache Memory Design Issues A Simulation-Based Study on Memory Design Issues for Embedded Systems Due to the increasing gap between the speed of CPU and memory cache designs have become an increasingly critical performance factor in microprocessor systems. Clients and servers are not distinguished from one another. They do not offer any.

Two important design issues for cache memory are. Power consumption and reusability d. A 10 Two important design issues for cache memory are A speed and volatility B.

Two important design issues for cache memory are Select one. Two important design issues for cache memory are ____. The simplest such organization is known as a two-level cache with the internal cache designated as level 1 L1 and the external cache designated as level 2 L2.

Most contemporary designs include both on-chip and external caches. A Technique for Improving the Lifetime of Non-volatile Caches. Two important design issues for cache memory are.

Use of NVM Non-volatile memory devices such as ReRAM resistive RAM and STT-RAM spin transfer torque RAM for designing on-chip caches holds the promise of providing a high. Course Title COMP 2004. Usually there are constraints on these factors based on the area of the chip and frequency targets.

This preview shows page 3 - 7 out of 185 pages. Cache Memory is a special very high-speed memory. Coherency Correct Answer D.

Two important design issues for cache memory are ____. Two important design issues for cache memory are Select one a speed and. It is the second level of cache memory that may present inside or outside the CPU.

When a replacement block of data is scan into the cache the mapping performs determines that cache location the block will occupy. 2- A message passing model is ____. 1- Two important design issues for cache memory are ____.

Two important design issues for cache memory are A speed and volatility B size. Recent papers in Cache Memory Design Issues. They are usually divided into multiple layers based on the architecture.

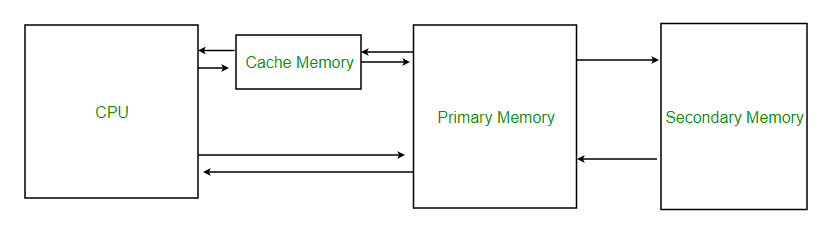

For L1 caches its very important that they be fast. Cache memory is an extremely fast memory type that acts as a buffer between RAM and the CPU. Size and replacement policy.

Pages 23 Ratings 100 5 5 out of 5 people found this document helpful. Size and access privileges O b. Whenever one CPU alters the data the cache of the other CPU must receive an updated version of this data.

Course Title CS 2301. Two important design issues for cache memory are ____. Block size Cache size Mapping function Replacement algorithm and Write policy.

L1 or Level 1 Cache. It is present in a small amount inside every core of the processor separately. Students who viewed this also studied.

Cache Memory Design. What are some other terms for kernel mode. Cache Memory Design Issues.

Speed and volatility B. Sohag University CIS MISC. School University of the People.

Size and access privileges. A speed and volatility B size and replacement policy C power consumption and reusability D size and access privileges Ans. The size of this memory ranges from 2KB to 64 KB.

Cache Size and Block Size To align with the processor speed cache memories are very small so that it takes less time to find and fetch data. Answers is the place to go to get the answers you need and to ask the questions you want. Size and replacement policy c.

A 10 two important design issues for cache memory are. Two constraints have an effect on the planning of the mapping perform. Two important design issues for cache memory are a.

Pages 185 Ratings 100 3 3 out of 3 people found this document helpful. Answer 1 of 6. Power consumption and reusability Which of the following is a property of peer-to-peer systems.

View full document. There are two design issues surrounding number of caches. This is called Cache A.

Pages 22 This preview shows page 3 - 7 out of 22 pages. It is used to speed up and synchronizing with high-speed CPU. A speed and volatility B size and replacement policy C power consumption and reusability D size and access privileges Ans.

On chip cache reduces the processors external bus activity and therefore speeds up. Cache memory is costlier than main memory or disk memory but economical than CPU registers. Two important design issues for cache memory are ____-size and access privileges-power consumption and reusability -size and replacement policy-speed and volatility.

It is the first level of cache memory that is present inside the processor. Cache Memory design represents the following categories. When it comes to the design issue of memory cache main problem is size and replacement policy be.

School Memorial University of Newfoundland. On chip cache accesses are faster than cache reachable via an external bus. Size and replacement policy Correct Answer.

Cache Memory In Computer Organization Geeksforgeeks

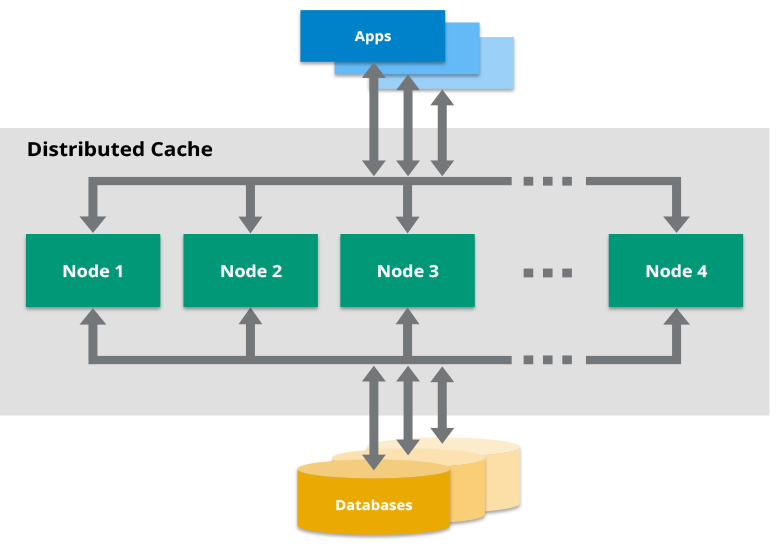

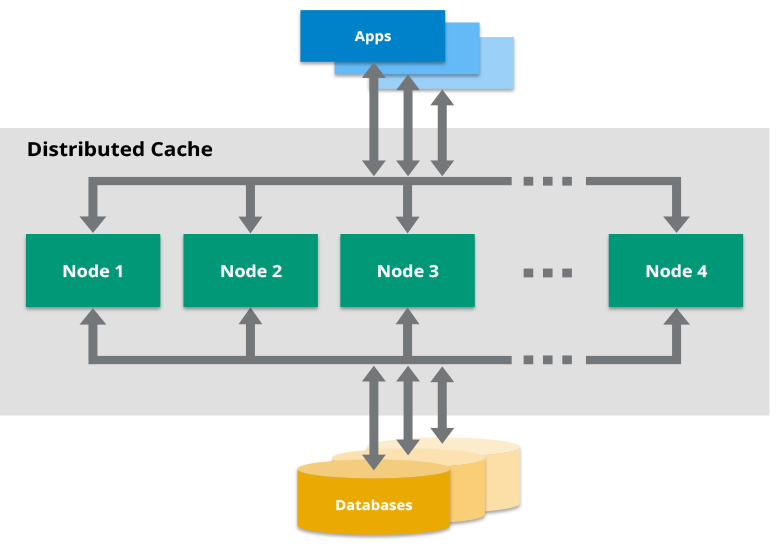

What Is A Distributed Cache Hazelcast

Cache Memory Design Geeksforgeeks

An Energy Efficient Dram Cache Architecture For Mobile Platforms With Pcm Based Main Memory Acm Transactions On Embedded Computing Systems

Set Associative Cache An Overview Sciencedirect Topics

Scratchpad Memory An Overview Sciencedirect Topics

0 comments

Post a Comment